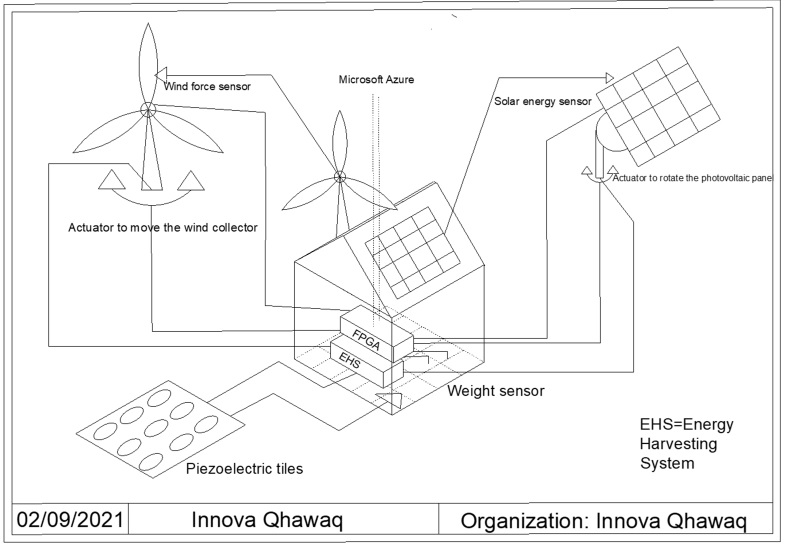

Our project has as its main concept, the maximum use of energy through the efficient obtaining of renewable sources within the home, from photovoltaic energy through solar panels that move intelligently through neural networks that seek the maximum use of sunlight, harvesting energy obtained from strategic places such as doors, windows and the floor; and wind energy obtained efficiently through artificial intelligence and adapted to the environment. Through the use of the D10-nano FPGA as a data processing center where the information obtained from the sensors of these energy sources sends signals to actuators so that the energy is obtained more efficiently through the exact orientation where it is collected. as much energy as possible, making the fpga work as a decision-making center to control these actuators, and also by using data storage intelligently in the cloud, neural networks will be used to optimize energy collection from sources and optimize the use of resources.

Project Proposal

1. High-level project introduction and performance expectation

The purpose of this design is to generate an intelligent proposal (efficient and sustainable) to the energy need that exists today, and that should reach all sectors of society, not only the industrial sector, but also the culture of energy sustainability. reach every home. The scope in terms of sociodemographic space is projected to any home, be it from the city in urban areas where it is intended to improve energy savings, as well as the homes of vulnerable populations or with economic deficiencies, where there is no electricity and sustainable alternatives can be implemented in order to have a decent quality of life. The target user is that user or users who are part of a home or families, who seek to improve their quality of life, either by minimizing the consumption of conventional electricity or people or households who live in areas where there is no electricity and this proposal is presented as an alternative to improve your quality of life.

Regarding the development of the design, fpga devices were considered, since they have a high flexibility in terms of design, which makes them adaptive processing units that, being programmed correctly, find better efficient responses to data processing, and through actuators, respond in the same efficient way, creating a powerful and innovative design.

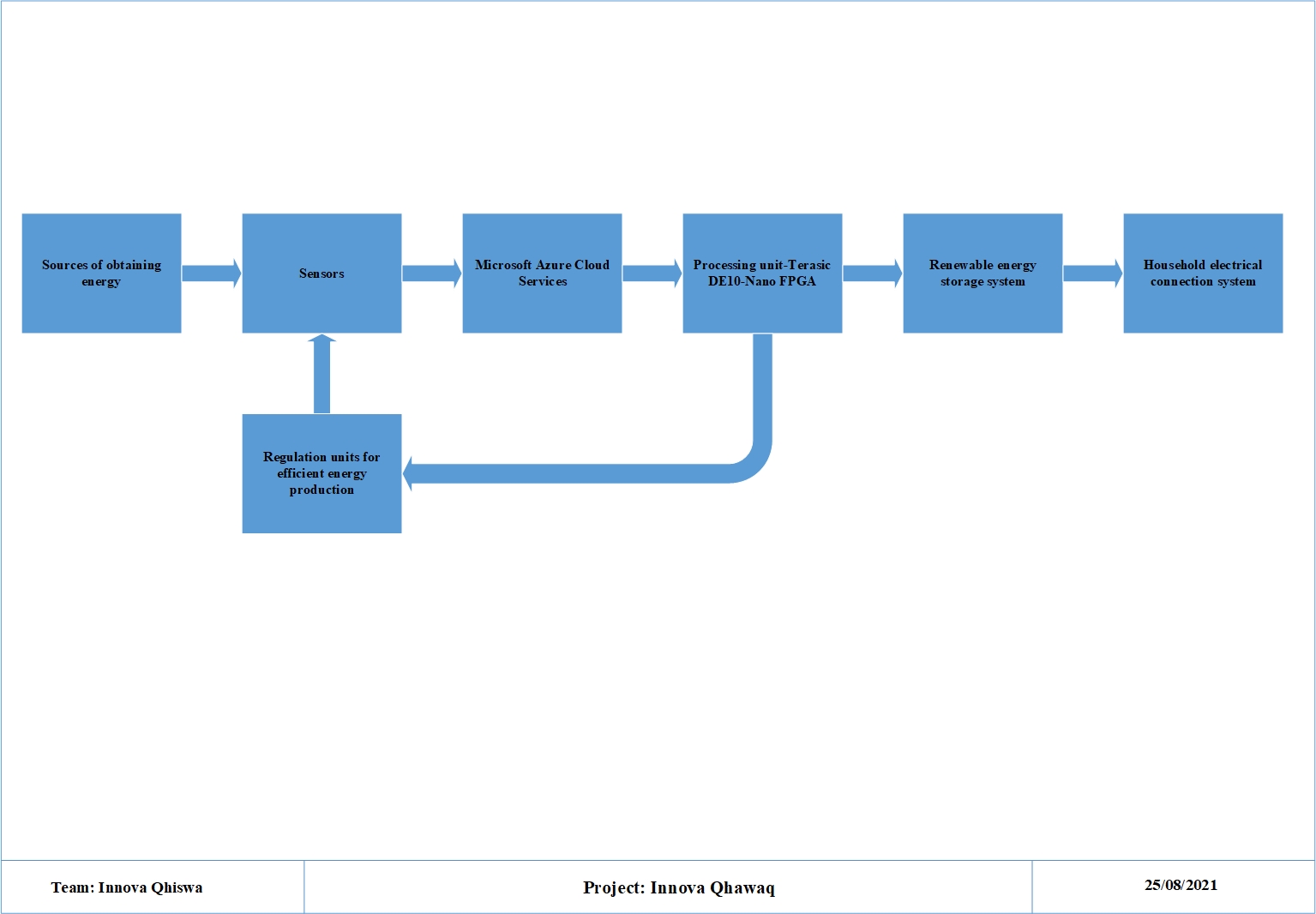

2. Block Diagram

3. Expected sustainability results, projected resource savings

The design seeks to minimize the use of conventional energy and generate an efficient energy collection model using energy collection alternatives, so the parameters used are:

- Decrease in the use of electrical energy by 70%

- Response to efficiency through correction of energy intake by actuators

- Fast data collection in the cloud

- speed in data processing to provide response in obtaining energy, through the use of fpga

4. Design Introduction

The sustainable energy collection system is based on the use of 3 types of renewable energy systems. Photovoltaic energy, wind energy and piezoelectric harvesting energy; The design of this high-level system is based on intelligent collection, through sensors that will process the best orientation of the energy source so that it is obtained and used in the most efficient way. This project is aimed at meeting the energy needs of vulnerable populations, as well as the replacement of conventional energy supply in urban areas, and also a possible industrial use.

5. Functional description and implementation

The implementation system is based on 3 types of renewable energy collectors, a wind turbine, photovoltaic panels and piezoelectric tiles. These elements will have a sensor that is oriented to where there is greater energy of the corresponding type, these data collected by the sensor will be sent from the FPGA (De10 nano) to the microsoft azure platform, they will be processed through neural networks and returned to the fpga so that it modifies the orientation of the energy collectors by means of actuators. In the case of piezoelectric tiles, it will be that the fgpa has sensitivity in the places of the house that have the greatest effect.

6. Performance metrics, performance to expectation

Conventional energy reduction: From 70% to 90%

Harvesting energy harvesting efficiency: up to 80%

Reliability of the system in terms of functional duration over time: 90%

What is sought is a sustainable model, which strengthens the way in which alternative forms of collection and use of energy are used.

7. Sustainability results, resource savings achieved

8. Conclusion

0 Comments

Please login to post a comment.