EM057 » SoC-based multipath GNSS receiver

Modern GNSS systems allow us to get our position with great accuracy without an advanced RF front-end. However, obtaining accurate position of a receiver is a challenging computational task. Combining power of fast parallel processing by FPGA and sequential processing by CPU allow us to implement complex algorithms for accurate real-time positioning.

The key feature of the project is signal multipath analysis, which allow the receiver to operate in difficult conditions and to perform reflectometry.

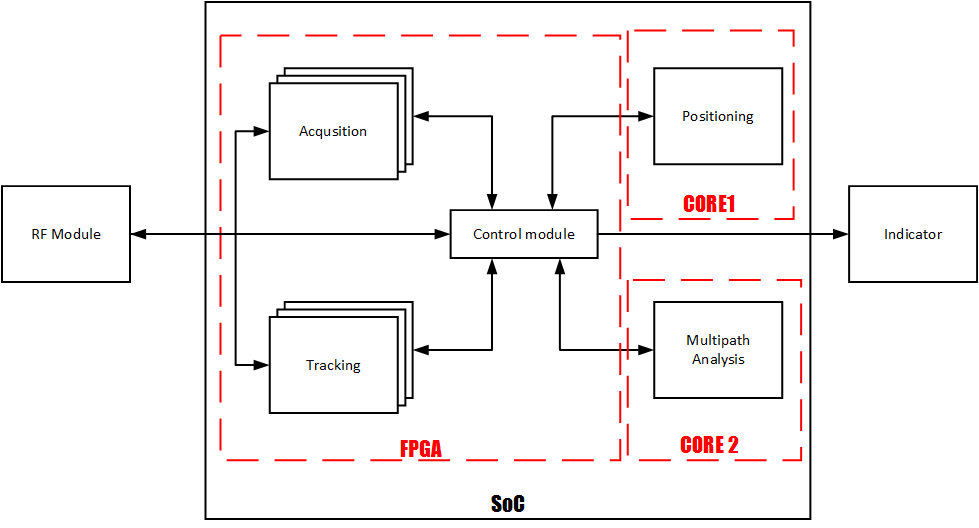

The general idea of this project is to create an FPGA-based GNSS receiver, using both advantages of programmable logic and computational power of embedded CPU cores. It would be necessary only to add a RF front-end chip and indicator to produce a complete GNSS receiver. Thus, we implement the elaborated algorithms of SDR and GNSS signal processing in two CPU cores and FPGA. The FPGA performs efficiently the part of the task, which allows the high level of parallelization. The complex computational algorithms are implemented in software and are being performed by CPU cores.

Fig 1. Contents

The main feature of the project is the better positioning in urban canyons. Traditional receivers often fail in these conditions because of the problems of signal propagation. The accuracy of positioning is poor due to the multipath effect. Proposed receiver analyzes reflected signal by using two antennas: one for a direct signal and another for reflected one. It can also be used to analyze reflection of a surface or even as a passive radar.

Fig. 2. Urban canyon

Animation 1. Receiving signals in urban canyons

A typical GNSS receiver performs the following operations: acquisition, tracking and position computation (see block diagram). At the acquisition stage, we acquire all available satellites and perform coarse estimation of code delay and Doppler shift. SoC implementation allows using the fastest algorithms in parallel.

The inexpensive antenna is used for direct signals and the antenna array for reflected signals. The navigational signals are firstly preprocessed by the RF front-end chips. The signal of each channel is digitized by its own ADC, thus at the output we have two flows of signal samples. The multichannel FPGA-based signal acquisition system, acquires all available satellites with an appropriate SNR. After a satellite was acquired, it is being tracked by an FPGA-based tracking system. Several parallel tracking channels perform accurate estimation of code delay and carrier phase, needed for further computations.

After a sufficient number of satellites are tracked, we need to get navigational data (ephemerides) and compute a position of the receiver. These algorithms are complex; therefore, it is reasonable to use a core-based implementation. It’s very convenient, that Cyclone-V SoC contains two ARM cores. One of them would be used for position computation. It consists mostly of linear algebra methods and complicated formulas. The FPGA-based peripherals might handle matrix operations. High performance core handles matrix definition and different transformations with complicated formulae, for example, transformation from Cartesian coordinates to geodetic coordinates. Another complicated task is Kalman filtration, which might give better results in some cases.

Another core solves the tasks of reflected signal analysis. Having information from several antennas with different polarization patterns allows us to analyze multipath effects. It could be useful in a situation when we receive a powerful reflected signal with an attenuated direct one. Reflection can take place almost from any object. The most considerable case is inside an urban canyon: there is a narrow open sky area for direct signal and all others are reflected signals from buildings.

Fig. 3. Multipath Effect

Animation 2. Signal multipath in 3D

GNSS signals have typically significantly less power than thermal noises, thus interference might affect the reception drastically. Multipath errors create another problem of positioning.

The analysis of reflected signals creates for a GNSS receiver many interesting opportunities of the improvement of the overall performance. Besides, such advanced receiver can be used as a passive radar.

The project combines power of parallelism provided by an FPGA, at the same time CPU cores enhance the power of computations for long complex algorithms. All mentioned above allows us to create a powerful GNSS receiver capable to use reflected signals to improve the accuracy of positioning. It is especially valuable in urban canyons and for solving specific tasks, like reflectometry.

Scheme of final real-time system.

Cyclone V SoCs have many IO pins. This feature provides good opportunities for future development of our project.

Firstly, it allows easy control of multiple RF Front-Ends with ADCs simultaneously at high sampling rate (tens of MSPS). FPGA-based implementation is also convenient for bitwise manipulations by the ADC’s conversion data. For example, it is possible to use efficiently just 2-3 bits of conversion results typically used in GNSS signal processing.

Secondly, many available IO pins allow us to simplify using wide buses for connection to external modules in order to create multisystem or multi-antenna systems. Our project is supposed to use GPS in various frequency bands (L1, L2C, and L5). However, we are planning to leave a scalability option to use also additional RF-modules for other GNSS systems (e.g. GLONASS, Galileo) or A-GPS to increase the accuracy of positioning. If resources of the single SoC are not sufficient, it is possible to use additional SoCs with external data buses.

Acquisition and tracking of various signals could be done using several hardware channels in parallel with identical algorithms of signal processing. Thus, we are going to implement acquisition and tracking using programmable logic, which significantly reduces processing time of acquisition and simplifies tracking. It also reduces time for reacquisition, when the signal is temporarily lost.

The FPGA part of the SoC also allows us to create custom calculation modules to boost the performance of the position computation and multipath analysis. However, these algorithms can hardly be implemented in FPGA completely, so built-in CPU cores will play their role as well. The integration of FPGA and CPU cores implies using custom peripheral modules implemented in programmable logic as parts of the CPU-based computational system. For example, we can implement necessary matrix operations of a certain type and resolution in such peripheral devices, which accelerates the algorithms of position computation. We expect that such approach will drastically improve overall performance of the device.

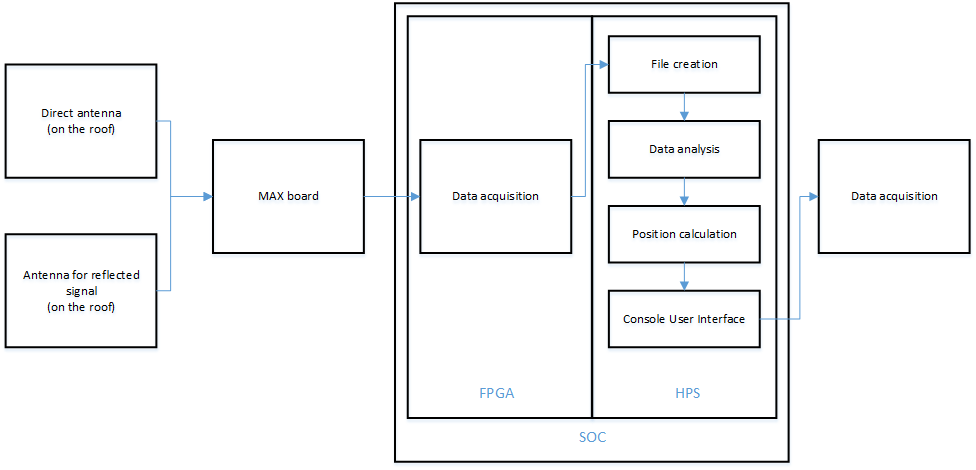

The purpose of this design was to start migrating from PC-based positioning to some portable solution of GNSS receiver. It consists of a RF frontend, FPGA-based data acquisition part and HPS-based data processing part.

Current version of the receiver uses two antennas: for direct and reflected signals. The RF front-end chips firstly preprocess the navigational signals. The FPGA part preprocess data, HPS calculates the position. During the preprocessing a file is created for future use. This file is used in positioning stage. The second antenna’s signal processing allows us to adjust weights for different satellites based on multipath analysis.

Originally, RF frontend was supposed to be based on Analog Devices’ software defined radio board. It already contains low noise amplifier, mixer and high speed ADC. However, AD rescinded their approval to send a board the last minute. Therefore, we have used the only thing we could manage to get before the deadline: a board based on MAX2120 and MAX19505. Its amplifier does not allow to use the board with simple antennas. Only stationary active antenna is sufficient.

The signal from antenna on the roof of our university goes through a coax cable to our SDR board. The output of MAX is 2-bit I and Q. These signals go to the DE10 nano. Originally, SoC was selected for the task because of its computational virtues. This temporary solution utilizes the FPGA part to preprocess signal and transfer it to an HPS’ bus.

The HPS runs an Angstrom Linux image. The software consists of two parts: first one gathers data over a predefined period of time and writes it to a file; the second one uses the file to calculate the receiver’s position.

This test version of receiver requires about 15-30s to acquire satellites, about a minute to track all available satellites, 10-30s to calculate position. Timings are not as promising as before because of not using FPGA-based custom peripherals, which are in plans for future.

SoC allows us to boost application: while the data is acquired, the two cores of HPS are free to do other tasks. For example, older data can be processed using 1st core and even older data – using the 2nd. Thus, we can calculate 3 time-delayed positions simultaneously.

Hardware structure of demo configuration:

Software flow: