EM103 » 2-D DCT/IDCT FPGA-based processor design for real-time image compression

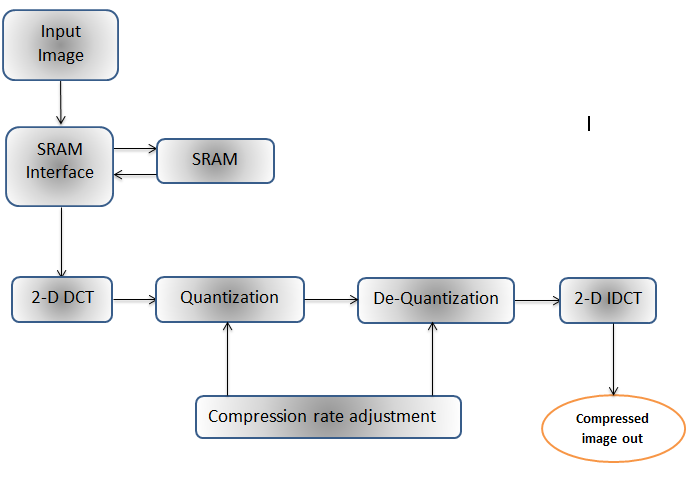

This project provides a processor design for the computation of DCT/IDCT transform that is used for image compression. the design algorithm is developed based on Madisetti and Willson model for the computation of DCT/IDCT. In addition, quantization and de-quantization stages, adopted in the JPEG standard of image compression, are also included to provide different image qualities for the convenience of different applications.

In digital signal processing, data compression plays a key role in reducing the size of data required to be stored, in a given amount of memory space, or to be sent through a telecommunication link. In other words, data compression has major applications in both signal processing and telecommunications. So that, saving both storage capacity and bit-rate is the main advantage of using data compression techniques.

The aim of our project is to build an embedded system, based on FPGA, which is able to apply compression on a 2-D image input and display the best image quality at a given bit-rate (or compression rate). Although most of the image processing systems are developed based on desktop pc, which is more generic for image processing applications, these systems may not meet the requirements of real-time performance. And since system performance has become bottle neck; FPGA solutions stand out widely.

There are different techniques for Data compression. We have implemented our compression algorithm based on the Discrete Consine Transformation DCT and the Inverse Discrete Cosine Transformation IDCT as well as the quantization and de-quantization stages. This method is used mainly in the JPEG standard for image compression.

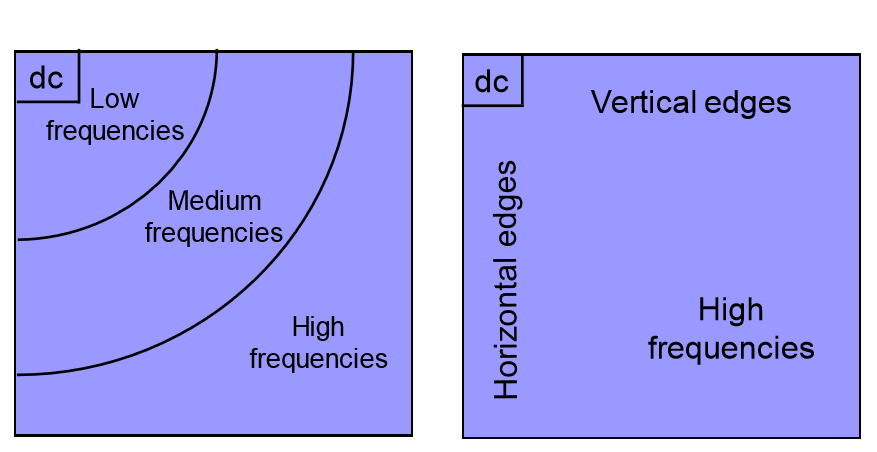

The importance of DCT comes from selecting it to be the basic transform coding method for the JPEG and MPEG standards. It helps separate the image into parts (or spectral sub-bands) of differing importance with respect to the spatial quality of the image as seen in the picture below. The more components included in white the more energy put around the corresponding frequency group.

This new permutation of the image frequency components and its energy distribution, done by the DCT, paves the way for the elimination of any undesired frequency components, such as high frequency components, when there is no need of them to show extra details. That is to say, the transformation preliminary process is so important for more dynamic adjustments of the target quality which varies according to the application.

The following picture shows some of the DCT features in arranging the frequency components of the input image and its ability in edge detection.

We, in our project, have implemented the computation model made by Madisetti and Willson. The input image block is chosen to be an 8*8 matrix which is replaced later by two 4*4 matrices due to the symmetry feature of the DCT. In such a way, an advantage of time complexity reduction comes from computing the DCT of two 4*4 matrices in parallel instead of one 8*8 matrix.

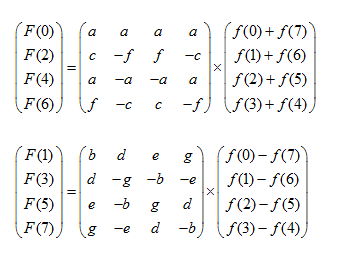

The matrix equation of the DCT computation model of Madisetti and Willson is given by:

Where:

acf and bdeg stand for the DCT coefficients.

The conduction of 2-D DCT (for a 2-D image input) will be based on computing 1-D DCT from the equation above two times in a row, one time for the rows of the input block and another time for its columns. So that, the number of logical elements consumed by the FPGA chip and time complexity will be reduced maximally.

The core of the computation process is to multiply the DCT coefficients matrix with an ordered input of image pixels.

The following figure shows the block diagram of computing 2-D DCT based on 1-D DCT

Figure -3-

The Inverse DCT can be processed similarly but with different coefficients.

As mentioned before, DCT/IDCT is important and considered as a preparatory process for compression. In our project, compression will be made mainly by quantization and de-quantization. Through which different qualities of the output image can be selected according to the target application. The output image can be displayed on a VGA monitor or a PC display screen interfacing to the FPGA kit or used for other applications

In conclusion, this design can offer many solutions in the context of signal processing and telecommunications. Its flexibility and independence built by FPGA technique has made it a competent choice in the world of embedded systems.